International Journal of Advanced Research in Computer and Communication Engineering Vol. 5, Issue 4, April 2016

# Review of 6T SRAM Technique for Reducing Power Consumption and Cost

# Manish Shrivastava<sup>1</sup> and Vimal Kishore Yadav<sup>2</sup>

Research Scholar, Electronics and Communication Engineering, Amity University, Madhya Pradesh, India<sup>1</sup>

A. Professor, Electronics and Communication Engineering, Amity University, Madhya Pradesh, India<sup>2</sup>

**Abstract:** With growing memory and processing needs of high performance systems, it is becoming important to have low power and efficient memory circuits as it constitutes more than 70% of circuit in a general purpose processor. Low static leakage current and higher noise immunity is major requirement of memory circuits in such systems. In this work we have conducted a regressive study of different FinFet based SRAM cells and compared the performance parameters of the selected cells. On the basis of study and comparison we have concluded a scope of work on which further research will be conducted.

Keywords: 6T SRAM, TMIG FinFet, IG FinFet, HSPICE, 7T SRAM.

# I. INTRODUCTION

As per present scenario SRAM is not that much popular as DRAM in use and there were many reasons behind that like here power consumption in SRAM than DRAM leakage in drain current, less readable and most importantly high cost. These are some issues which are lagging users to use SRAM but if by fixing these issues of power consumption, leakage current , the cost of SRAM is successfully becomes lesser than DRAM and it became more user friendly.

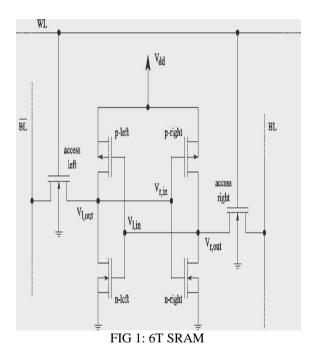

The 6 transistor SRAMs is made up by using CMOS technology, but while shrinking it to below 100nm there are some leakage current, high power consumption, probability of reading failure found and it becomes unstable. To drag away these issues we use FINFET technology which will reduce leakage current. The 6 transistor SRAMs, based on Schmitt trigger using FINFET technology reduce the probability of read failure at lower supply voltage by changing the threshold of the circuit. This Schmitt trigger circuit is used as a drop in place of invertors in 6 transistor SRAM cell.

The read/write (R/W) memory circuits are intended to allow the composing in the memory cell, also as their recovery on request. The memory circuit is said to be static if the put away information can be held uncertainly (for whatever length of time that adequate power voltage is given), with no requirement for an occasional invigorate operation. The data stock storage cell or The 1-bit memory cell in static RAM constantly comprises of a straight forward lock circuit with stable working focuses (states).

SRAM cell essentially has 3 methods of operation, 1.Hold mode, 2.Write mode, 3.Read mode. In the hold mode the information is put away in the cell and in the write mode the information is composed onto the cell from the bit lines and in the read mode the information is perused on the bit lines.

#### **II. FINFET (FIN FIELD EFFECT TRANSISTOR)**

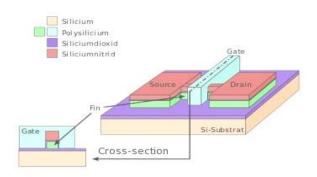

FinFet, otherwise called Fin Field Effect Transistor, is a kind of non-planar or "3D" transistor utilized as a part of the outline of cutting edge processors. As in prior, planar outlines, it is based on a SOI (silicon on protector) substrate. Notwithstanding, FinFet plans likewise utilize a directing channel that ascents over the level of the protector, making a flimsy silicon structure, formed like a balance, which is known as a door anode. This balance molded terminal permits numerous doors to work on a solitary transistor.

This kind of multi-entryway process broadens Moore's law, permitting semiconductor makers to make CPUs and memory modules that are littler, perform quicker, and

International Journal of Advanced Research in Computer and Communication Engineering Vol. 5, Issue 4, April 2016

devour less vitality. Intel started discharging FinFet CPU innovation in 2012 with its 22-nm Ivy Bridge processors.

Fig: 2 Schematic diagram of FinFet

# ADVANTAGES OF FINFET TECHNOLOGY

Here are some advantages of FinFet technology which will enhance the parameters of SRAM whether it was power or some other things are described below.

- Much lower power utilization permits high combination levels. Early adopters reported 150% enhancements.

- FinFets work at a lower voltage as an after effect of their lower threshold voltage.

- Regularly lessened by up to 90%

- Regularly in overabundance of 30% quicker than the non-FinFet variants.

After the advantages and need of SRAM, we discussed about some FinFet technology based SRAM

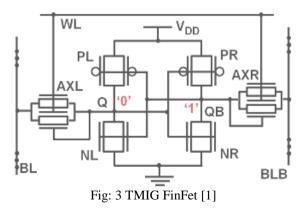

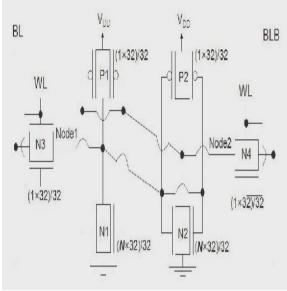

# III. TRI-MODE INDEPENDENT GATE (TMIG) FINFET

In this TMIG FinFet [1], the strength of AXR with BG connected to QB = "1" is twice the AXR in a TG FinFet SRAM. This increases the trip point of the inverter formed by PR, NR, and AXR and therefore, tends to increase the read stability. According to [4] VLSI interconnects every circuit is used to reduced noise and physical design with the help of an efficient technique for estimation of coupled noise in on-chip. As indicated by [6] Beta distribution is a probability function technique by which we can collect the delay of any circuit which having VLSI interconnects.

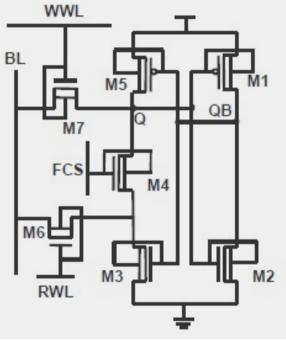

#### IV. 7T SRAM CELL

Between the writability of the cell at ultra low voltage power supply and write assist at 20nm technology node the breaking up of feedback between the true storing nodes is includes in the FinFet 7T SRAM [2], process variations in sub threshold region becomes more stable due to the read decoupling and feedback cutting in 7T SRAM.

Here m4 is used to reduce pull-up strength to achieve better writability without using boosting techniques. In VLSI based circuit each and every technique is used for maximizing the strength of the device. According to [5] PERI (Probability distribution function Extension for Ramp Inputs) technique that extends delay metrics for ramp inputs to the more general and realistic non-step inputs.

Fig: 4 7T SRAM [2]

#### V. IG FINFET BASED SRAM

According to the independent-gate (IG) FinFet SRAM cell [3] during read operation it activates one of the gates from double gate data access transistors.

After intensely extending the edge voltage of the passageway transistor in 6T SRAM cell topology then the unsettling impact brought on in light of the prompt data access instrument has been basically reduced.

Because of this average read static noise margin of the sample with independent gate bias technique is become higher and also the average leakage power and the cell area of the IG FinFet SRAM circuit have been reduced.

A methodology [7] for modifying and fitting the snippets of the motivation reaction to likelihood thickness works to decide the delay accurately at an early stage.

International Journal of Advanced Research in Computer and Communication Engineering Vol. 5, Issue 4, April 2016

Fig: 5 IG FinFet [3]

| VI. RESULTS AND SIMULATION |              |                 |

|----------------------------|--------------|-----------------|

| Technology                 | Voltage (mV) | Read<br>SNM(mV) |

| 7T SRAM                    | 0.7          | 0.12185         |

| TMIG                       | 0.7          | 1.01            |

| IG                         | 0.7          | 0.12            |

# VII. CONCLUSION

After the all regressive study and research it is found that after modifying the circuit of SRAM we can increase its performance and reliability at much extent. Cost of SRAM can also be effectively reduced. As we can see that in day to day scenarios embedded and internet of things (IOT) devices are taking a key role part in advancing the technologies and this can be a great step to provide them cheaper, effective and reliable SRAM.

#### REFRENCES

- Sumeet Kumar Gupta, Jaydeep P. Kulkarni, Kaushik Roy, "Tri-Mode Independent Gate FinFet-Based SRAM", 'IEEE transactions on electron devices, vol. 60, no. 11, november 2013

- [2]. C. B. Kushwah, S. K. Vishvakarma, D. Dwivedi, "Single-Ended Sub-threshold FinFet 7T SRAM," 978-1-4799-2153-9/14/\$31.00 ©2014 IEEE

- [3]. Zhiyu Liu, Sherif A. Tawfik, and Volkan Kursun, "Statistical Data Stability and Leakage Evaluation of FinFet SRAM Cells with Dynamic Threshold Voltage Tuning under Process Parameter Fluctuations," 9th International Symposium on Quality Electronic Design.

- [4]. Vikas Maheshwari, Shruti Gupta, Kapil Khare, Vimal Yadav, Rajib Kar, Durbadal Mandal, Anup Kr. Bhattacharjee, "Efficient Coupled Noise Estimation for RLC On-Chip Interconnect", IEEE Symposium on Humanities, Science and Engineering Research (SHUSER-2012), Kuala Lumpur, Malaysia, pp. 1125-1129,June 24-27, 2012

- [5]. Vikas Maheshwari, Prabhakar Sharma, Alka Goyal, Vimal K Yadav, Sampath Kumar, "Closed Form Expressions for Delay to Ramp Inputs for On-Chip VLSI RC Interconnect", National

Conference on Emerging Trends in Electrical, Instrumentation & Communication Engineering, vol. 4, Issue 7 ISSN 2222-1727, (Paper) ISSN 2222-2871 (Online), 2013

- [6]. Vimal Kishore Yadav, Pratiksha Singh Gaur, Sucheta Yadav, "Impending Form Interpretations for Delay to Ramp and Step Input On-Chip VLSI RLC Annex", "International Journal of Advanced Research in Computer and Communication Engineering(IJARCCE)", vol. 3, Issue 11, ISSN (Online) : 2278-1021,ISSN (Print) : 2319-5940,2014

- [7]. Vimal Kishore Yadav, Priyanka Thapak, Sucheta Yadav, "Effect of Ramp Input on RLC Interconnect In Modern VLSI Design", "International Journal of Scientific Research Engineering & Technology (IJSRET)", vol. 3, Issue 8, ISSN 2278 – 0882,2014.